平台一

实验平台地址:http://grs.nscscc.com:18000

Gitlab地址:http://grs.nscscc.com:18001

平台二(暂时关闭,之前提交的比赛结果依旧有效)

实验平台地址:http://58.49.29.194:8000

Gitlab地址:http://58.49.29.194:8001

平台三(无法TCP连接串口和在线调试)(暂时关闭,之前提交的比赛结果依旧有效)

实验平台地址:http://r.nscscc.org:23465

Gitlab地址:http://r.nscscc.org:23466

自主CPU设计虚实联动教学平台

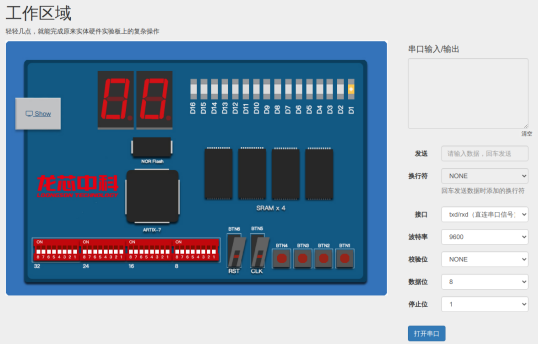

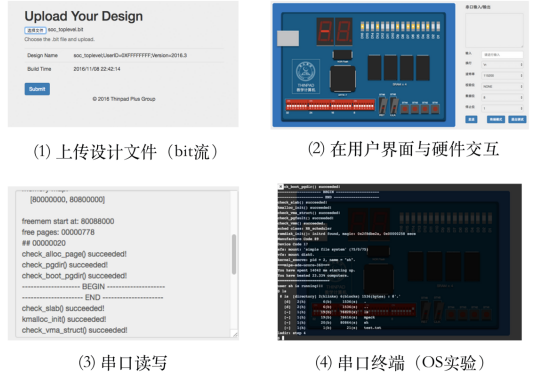

自主CPU设计虚实联动教学平台可满足高等院校计算机专业本科生开设的《数字逻辑》、《计算机组成原理》、《计算机体系结构》等计算机基础软硬件课程的实验教学需要。借助强大的 SoC 和FPGA ,远程教学实验平台可以提供丰富的远程实验功能,并可为学生提供与线下实验高度一致的实验过程和实验结果。不管学生是在家还是在宿舍都不影响实验课程的开展。

产品组成和介绍

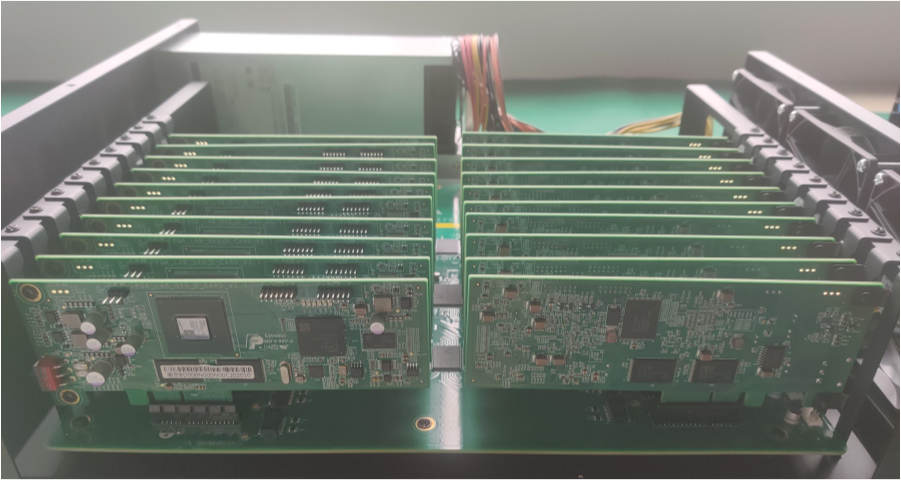

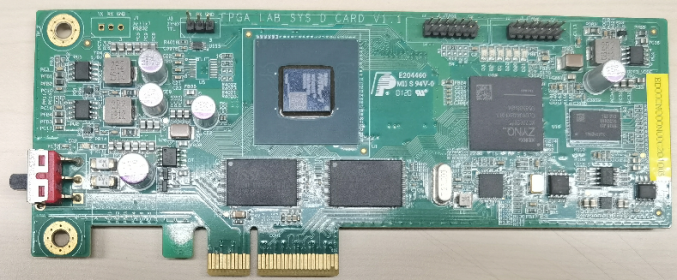

自主CPU设计虚实联动教学平台由20个实验板、一个机箱和一个服务器组成。实验板由载板和子板组成,载板主要起到网络交换功能。子板由实验子系统和控制子系统组成,实验子系统包括Xilinx Artix-7系列FPGA 、4颗1 MB 16位SRAM、1颗64MB NOR FLASH、简单I/O组件。控制子系统包括Zynq-7000 SoC、1颗2Gb DDR3 SDRAM、1颗千兆Phy芯片。

所有的用户交互和实验管理工作都在服务器上进行处理,而用户实现的 FPGA 逻辑则运行在实验板上。登录后,每个用户将被分配到一个实验板。

每个实验板由两个子系统组成:实验子系统和控制子系统。所有实验子系统的资源是开放给分配使用这个实验板的用户的。控制子系统监控实验子系统,并且在实验子系统和服务器之间交换数据。

产品功能介绍

教师管理

实验内容

发表回复